ProASICPLUS Flash Family FPGAs

4- 6

v5.9

v2.0

(continued)

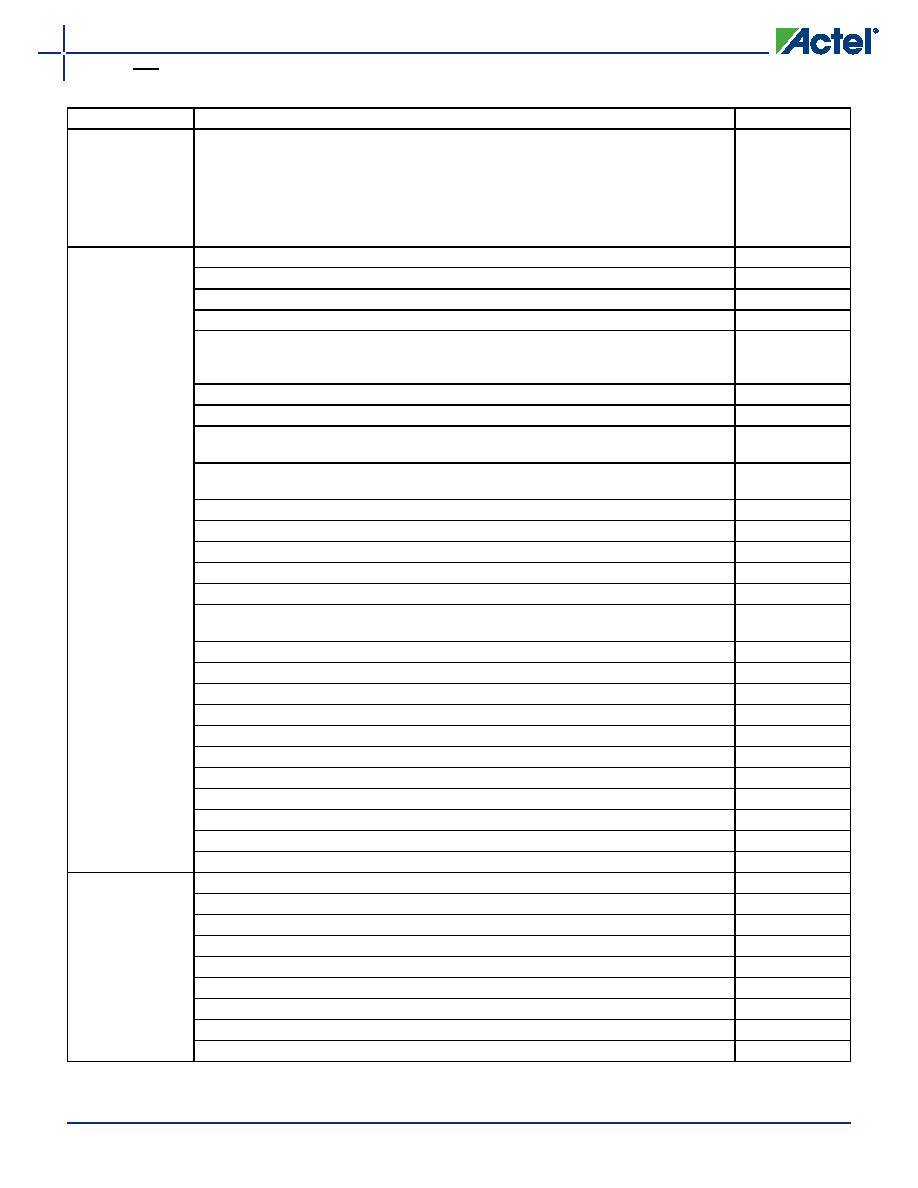

The following pins have been changed in the "1152-Pin FBGA" table:

Pin Number

Function

Pin Number

Function

U4

I/O (GLMX1)

U29

NPECL2

U6

NPECL1

U31

I/O (GLMX2)

U7

GL1

V28

PPECL2 (I/P)

V5

GL2

V29

GL4

V6

PPECL1 (I/P)

V30

GL3

3-69

Advance v0.7

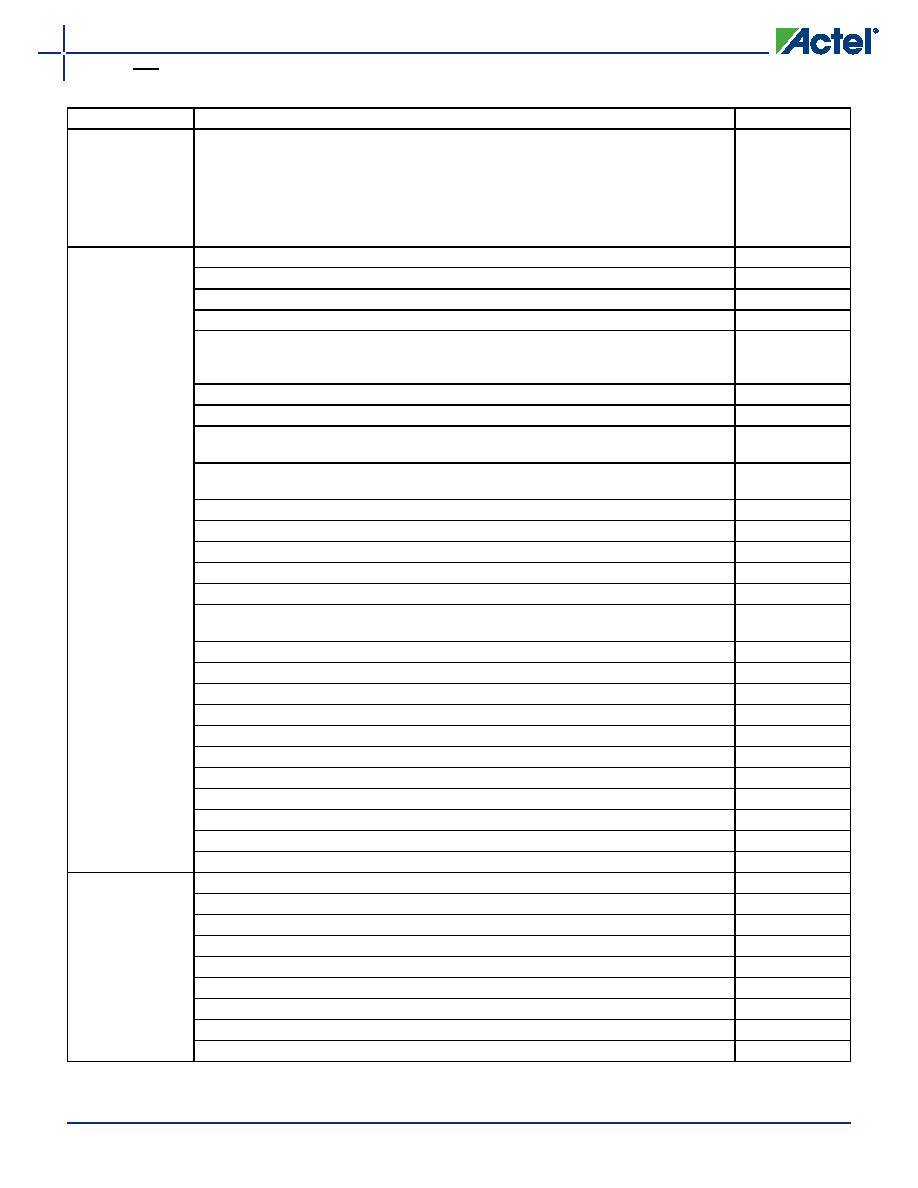

The "ProASICPLUS Architecture" section was updated.

1-2

The "Array Coordinates" section and Table 2-2 Array Coordinates are new.

2-5

The "Power-Up Sequencing" section is new.

2-7

"I/O Features" section was updated.

2-6

The "Timing Control and Characteristics" section was updated. "Physical Implementation"

section, "Functional Description" section, "Lock Signal" section, and "PLL Configuration

Options" section are new.

2-10 to 2-13

"PLL Block – Top-Level View and Detailed PLL Block Diagram" section was updated.

2-11

Figure 2-12 Input Connectors to ProASICPLUS Clock Conditioning Circuitry was updated.

2-12

"Sample Implementations" section, "Adjustable Clock Delay" section, and the "Clock Skew

Minimization" section are new.

2-13

Figure 2-13 Using the PLL 33 MHz In, 133 MHz Outthrough and Figure 2-17 Using the PLL

for Clock Deskewing are new.

2-14 to 2-16

The "PLL Electrical Specifications" section is new.

2-18

The "Design Environment" section was updated.

2-25

Figure 2-23 Tristate Buffer Delays was updated.

2-42

The "Calculating Typical Power Dissipation" section was updated.

2-28

The "DC Electrical Specifications (VDDP = 2.5 V ±0.2V)" section was updated.

2-34

The Table 2-24 DC Electrical Specifications (VDDP = 3.3 V ±0.3 V and VDD = 2.5 V ±0.2 V)

Applies to Military Temperature and MIL-STD-883B Temperature Only was updated.

2-38

The "DC Specifications (3.3 V PCI Operation)1" section was updated.

2-40

The "Tristate Buffer Delays" section (the figure and table) have been updated.

2-42

The "Output Buffer Delays" section (the figure and table) have been updated.

2-44

The "Input Buffer Delays" section was updated.

2-46

The "Global Input Buffer Delays" section was updated.

2-48

The "Predicted Global Routing Delay" section was updated.

2-50

The "Global Routing Skew" section was updated.

2-50

The "Sample Macrocell Library Listing" section was updated.

2-51

The "Pin Description" section was updated. GLMX is new.

2-73

The "Recommended Design Practice for VPN/VPP" section was updated.

2-74

Pin AK31 of FG1152 for the APA1000 changed to VPP.

3-69

Advance v0.6

The "Features and Benefits" section were updated.

i

The "ProASICPLUS Product Profile" section was updated.

i

The "Ordering Information" section was updated.

ii

The "Plastic Device Resources" was updated.

ii

The "ProASICPLUS Architecture" section was updated.

1-2

Table 2-1 Clock Spines was updated.

2-4

Figure 2-11 PLL Block – Top-Level View and Detailed PLL Block Diagram was updated.

2-11

The "Design Environment" section was updated.

2-25

The "Package Thermal Characteristics" section was updated.

2-27

Previous version

Changes in current version (v5.9)

Page